Welcome to Edge AI Implementation Memo

This blog is a memo for recording the implementation process of embedded AI technology.

Posts

-

Introduction

Notes on running SAM2 video inference on Jetson Orin Nano

-

Introduction

This document is a memo on using Xilinx-provided IP, namely the MIPI CSI-2 Rx Subsystem and MIPI DSI Tx Subsystem.

-

Introduction

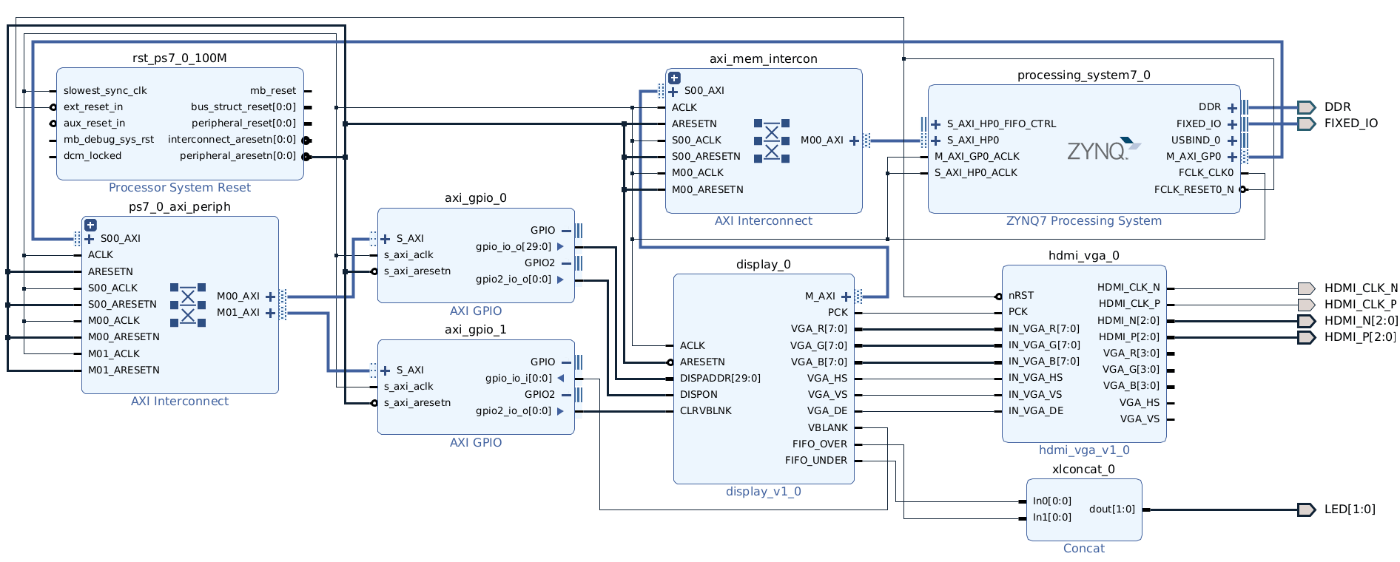

This post documents the implementation steps described from Chapter 9 onward in the referenced book

-

Introduction

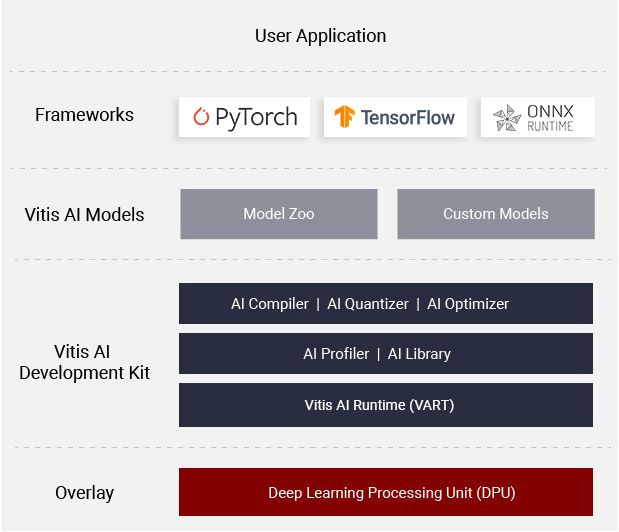

This is a memo outlining the basic steps to run a DNN model using Vitis AI and Zynq MPSoC, as I had forgotten many details after a long break. It’s easy to forget FPGA-related procedures each time.

-

Introduction

This post continues from the previous one, documenting the practical application of “High-Level Synthesis Applications” from Chapter 11-1 onward in “FPGA Programming Complete Guide, 2nd Edition”.

subscribe via RSS